# Chapitre 2 : Jeu d'instructions du 6809

On peut classer les instructions du 60809 en six catégories principales :

- Instructions de transfert de données

- Instructions de traitement de données

- Instructions de pointeurs de données

- Instructions de tests et branchements

- Instructions d'entrées-sorties

- Instructions de commandes

#### 1. - Instructions de transfert de données

Les instructions de transfert de données transmettent des données entre :

- les registres internes du 6809;

- les registres internes et la mémoire;

- les pointeurs.

#### 1.1. Instructions de transfert sur les registres internes

Les instructions **EXG** et **TFR** permettent le transfert de données entre les registres internes. Le transfert ne peut se faire que sur des registres de même taille.

**EXG R1,R2** Les contenus des registres R1 et R2 sont échangés. Exemple : EXG

A,DP

**TFR R1,R2** Le contenu du registre R1 est transféré dans le registre R2.

Exemple: TFR D,X

## 1.2 Instructions de transfert sur les registres internes et la mémoire

Les instructions **LD** (**LOAD** : **charger**) et **ST** (**Store** : **stocker**) permettent le transfert de données entre les registres internes et la mémoire.

| Instruction | Fonction                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------|

| LD          | la donnée en mémoire est chargée dans le registre spécifiée                                                  |

| ST          | Le contenu du registre interne spécifié dans l'instruction est transféré dans l'emplacement mémoire indiqué. |

Exemple:

LDA \$1000 charger l'accumulateur A avec le contenu de \$1000

STA \$2000 Stocker le contenu de l'Acc. A à l'adresse mémoire \$2000

#### 1.3 Instructions de transfert sur les pointeurs

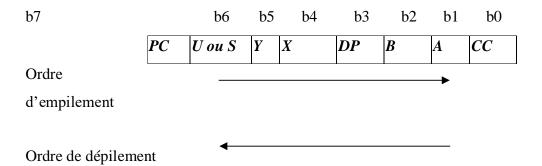

Les instructions **PUSH** (**empiler**) et **PULL** (**dépiler**) permettent le transfert des registres internes dans la pile en mémoire. Les registres à **empiler/dépiler** sont indiqués dans l'octet (post octet) qui suit immédiatement le code opération de l'instruction **PUSH/PULL**. Chaque bit du post octet indique un registre interne

Quand un de ces bits vaut 1, le registre correspondant est empilé/dépilé. Le pointeur de pile spécifié dans l'instruction ne peut être empilé/dépilé. Chaque fois qu'un octet est mis dans une pile, le pointeur de pile est décrémenté de 1. Pour un registre de 16 bits, on empile d'abord l'octet de poids faible dans la pile. Le dépilement est identique excepté qu'il incrémente le pointeur de pile.

| Instruction | Fonction                                   |

|-------------|--------------------------------------------|

| PUL         | Dépilement de(s) registre(s) de la pile.   |

| PSH         | Empilement de(s) registre(s) dans la pile. |

# Exemple:

PSHS #\$FF

| ssss - C ssss - B ssss -A ssss -9 | CC      |

|-----------------------------------|---------|

| ssss - 8                          | Α       |

| ssss - 7                          | В       |

| ssss – <b>6</b>                   | DP      |

|                                   | X-haut  |

| ssss - 5                          | X-bas   |

| ssss – <b>4</b>                   | Y-haut  |

|                                   | Y-bas   |

| ssss - 3                          | U-haut  |

| ssss - 2                          | U-bas   |

| ssss - 1                          | PC-haut |

| SSSS                              | PC-bas  |

|                                   |         |

|                                   |         |

|                                   |         |

## 2. - Instructions de traitement de données

Les instructions de traitement de données peuvent être classées en quatre catégories :

- les instructions arithmétiques;

- les instructions logiques;

- les instructions de déplacements (rotation et de décalage);

- Les instructions d'incrémentation/décrémentation, mise à zéro, complémentation

# 2.1. Instructions arithmétiques

Les instructions arithmétiques sont listées dans le tableau suivant :

| Instruction | Fonction                                                       |  |

|-------------|----------------------------------------------------------------|--|

| ADD         | Addition du contenu mémoire à un accumulateur                  |  |

| ADC         | Addition du contenu mémoire à un accumulateur avec retenue     |  |

| ABX         | Addition de l'accumulateur B à X                               |  |

| DAA         | Ajustement décimal de l'acc. A                                 |  |

| MUL         | Multiplication de A par B (non signée)                         |  |

| SUB         | Soustraction du contenu mémoire à un accumulateur              |  |

| SBC         | Soustraction du contenu mémoire à un accumulateur avec retenue |  |

| SEX         | Extension de signe de l'accu. B à l'acc. A                     |  |

## 2.2. Instructions logiques

Les instructions logiques sont listées dans le tableau suivant :

| Instruction | Fonction                                       |  |

|-------------|------------------------------------------------|--|

| AND         | 'ET logique' entre mémoire et registre interne |  |

| EOR         | 'XOR' entre mémoire et registre interne        |  |

| OR          | 'OU logique' entre mémoire et registre interne |  |

L'instruction AND est utile pour mettre à 0 ou masquer un ou plusieurs bits dans un mot. L'instruction XOR est utile pour des comparaisons. On peut l'utiliser aussi pour complémenter un mot (EORA #\$FF).

#### **2.3.** Instructions de déplacements (rotation et de décalage)

Il faut tout d'abord distinguer entre une opération de décalage et une opération de rotation.

Dans une opération de décalage, tous les bits sont décalés d'une position vers la droite ou vers la gauche. Le bit qui sort du registre va dans le bit de retenue C; le bit qui entre est un zéro.

Dans une opération de rotation, le bit entrant dans le registre est celui qui provient de la retenue C.

| Instruction | Fonction                                                                                                   |

|-------------|------------------------------------------------------------------------------------------------------------|

| ASR         | Décalage arithmétique à droite.                                                                            |

|             | Les bits sont décalés vers la droite. b <sub>0</sub> est transféré vers C et b <sub>7</sub> reste inchangé |

| LSL ou ASL  | Décalage logique ou arithmétique à gauche.                                                                 |

|             | Les bits sont décalés vers la gauche. b7 est transféré vers C et b0 est mis à 0.                           |

| LSR         | Décalage logique à droite.                                                                                 |

|             | Les bits sont décalés vers la droite. b <sub>0</sub> est transféré vers C et b <sub>7</sub> est mis à 0.   |

| ROL         | Rotation à gauche                                                                                          |

|             | Les bits subissent une rotation vers la gauche. b <sub>7</sub> est transféré vers C et la                  |

|             | valeur d'origine de celui-ci est transférée vers b <sub>0</sub> .                                          |

| ROR         | Rotation à droite <sup>2</sup>                                                                             |

|             | Les bits subissent une rotation vers la droite. b <sub>0</sub> est transféré vers C et la valeur           |

|             | d'origine de celui-ci est transférée vers b7.                                                              |

Exemple:

RORA; ROLB; LSRA; LSRB

# 2.4 Instructions d'incrémentation/décrémentation, Mise à zéro, Complémentation

Ces instructions sont listées dans le tableau suivant :

| Instruction | Fonction                                               |

|-------------|--------------------------------------------------------|

| CLR         | Remise à 0 du contenu mémoire ou de l'accumulateur     |

| DEC         | Décrémentation du contenu mémoire ou de l'accumulateur |

| INC         | Incrémentation du contenu mémoire ou de l'accumulateur |

| COM         | Complément à 1 du contenu mémoire ou de l'accumulateur |

| NEG         | Complément à 2 du contenu mémoire ou de l'accumulateur |

| NOP         | Pas d'opération. Incrémentation du compteur programme  |

## 3. Instructions de tests et branchements

Les instructions de tests et branchements peuvent être classées en trois catégories :

- les instructions de tests et de comparaison;

- les instructions de tests et branchements;

- les instructions de test et branchement

#### 3.1 Instructions de tests et de comparaison

Ces instructions sont utilisées pour réaliser des tests de bits d'état et des comparaisons afinde pouvoir prendre des décisions au cours du déroulement d'un programme dépendant de la valeur de ces indicateurs. Seul le registre d'état est modifié ; ni le registre spécifié ni l'opérandeen mémoire ne sont changés. Aucun branchement n'est effectué.

Ces instructions sont listées dans le tableau suivant :

| Instruction | Fonction                                                                       |  |  |  |

|-------------|--------------------------------------------------------------------------------|--|--|--|

| BIT         | Test de bits BITA M; BITB M                                                    |  |  |  |

|             | L'acc. (A ou B) spécifié et l'opérande en mémoire font l'objet d'un ETlogique. |  |  |  |

| CMP         | Comparaison d'un contenu mémoire avec un accumulateur <b>CMPA CMPB</b>         |  |  |  |

|             | ACCX – M                                                                       |  |  |  |

| TST         | Test du contenu mémoire ou d'un accumulateur TSTA; TSTB; TST M                 |  |  |  |

|             | ACCX - 0; $M - 0$                                                              |  |  |  |

#### 3.2 Instructions de test et branchement

Ces instructions effectuent des tests sur 4 indicateurs du registre d'état (C, N, Z, V) afin de réaliser des branchements au cours du déroulement d'un programme dépendant de la valeur de ces indicateurs. Deux types de branchement existent :

- Un branchement cours : déplacement entre -128 et +127

- Un branchement long : déplacement entre –32768 et +32767.

Les instructions utilisant un branchement long ont une lettre 'L' qui précède leurs mnémoniques.

Ces instructions sont listées dans le tableau suivant :

| Instruction | Fonction                                  |                            |              |    |   |

|-------------|-------------------------------------------|----------------------------|--------------|----|---|

| BCC ou BHS  | Branchement si pas de retenue BC          | CN;LBC                     | C NN         |    |   |

|             | Si C=0, alors : PC $PC + N$ (ou)          | _                          |              |    |   |

| BCS ou BLO  | Branchement si retenue BC                 | S N ; LBC                  | S NN         |    |   |

| BEQ         | Branchement si égal à zéro                | Branchement si égal à zéro |              |    |   |

| BNE         | Branchement si différent de zéro          |                            |              |    |   |

| BGE         | Branchement si supérieur ou égal à zéro ( | signé)                     |              |    |   |

|             | Si $(N \oplus V)=0$ alors : PC PC + NN    | V (ou)                     | PC           | PC | + |

| BLT         | Branchement si inférieur (signé)          |                            | _            |    |   |

| BGT         | Branchement si supérieur (signé)          |                            | $\leftarrow$ |    |   |

| 3 BLE | Branchement si inférieur ou égal (signé)     |  |

|-------|----------------------------------------------|--|

| ВНІ   | Branchement si supérieur (non signé)         |  |

| BLS   | Branchement si inférieur ou égal (non signé) |  |

| BMI   | Branchement si négatif                       |  |

| BPL   | Branchement si positif                       |  |

| BVC   | Branchement si pas de débordement            |  |

| BVS   | Branchement si débordement                   |  |

# 4. instructions de traitement des interruptions

Le tableau suivant illustre ces instructions :

| Instruction                                               | Fonction                                             |                    |  |

|-----------------------------------------------------------|------------------------------------------------------|--------------------|--|

| CWAI Mise à zéro d'indicateurs d'état et attente d'intern |                                                      | uption <i>CWAI</i> |  |

|                                                           | CC = CC and N. Ceci peut mettre à 0 certains bits de |                    |  |

|                                                           | démasquer les interruptions.                         |                    |  |

| SYNC                                                      | Synchronisation avec une ligne d'interruption        | SYNC               |  |

| RTI                                                       | Retour de sous-programme d'interruption              | RTI                |  |

| SWI/SWI2/SWI3                                             | Interruptions logicielles                            |                    |  |

|                                                           | L'état complet est sauvegardé dans la pile sy        | stème.             |  |

| СНА | PITRE 2      |   | JEU D'INSTRUCTION DU 6809 |

|-----|--------------|---|---------------------------|

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     |              |   |                           |

|     | Dr. K.CHAKER | 8 |                           |