## Boucle à verrouillage de phase

### 1. Rappel

Soit un signal sinusoïdal de la forme :  $v(t) = V \sin \phi(t) = V \sin(\omega t + \varphi)$

La phase instantanée :  $\phi(t)$ .

La pulsation instantanée :  $\Omega(t) = \frac{d\phi(t)}{dt} = \omega + \frac{d\varphi(t)}{dt}$ .

La fréquence instantanée du signal est :  $f(t) = \frac{1}{2\pi} \frac{d\phi(t)}{dt}$ .

### 2. Définition d'une boucle à verrouillage de phase

La boucle à verrouillage de phase (PLL pour Phase Locked Loop) est un système électronique qui permet de synchroniser la phase instantanée  $\phi_e(t)$  d'un oscillateur local à la phase instantanée  $\phi_s(t)$  d'un signal extérieur pris comme référence.

Selon les signaux qu'il faut traiter, il existe plusieurs types de PLL : analogique, numérique, hybride, logicielle. Dans ce qui suit, on s'intéresse au PLL analogique.

### 3. Schéma de principe

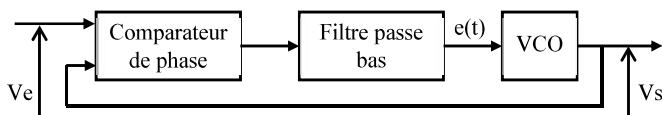

Une boucle à verrouillage de phase est composée d'un comparateur de phase, d'un filtre passe bas et d'un VCO :

Figure 1 : Schéma de principe d'une boucle à verrouillage de phase.

Le comparateur de phase fournit une tension proportionnelle à la différence entre les phases d'un signal externe connecté à l'entrée de la PLL et le signal fourni par le VCO. Dans le cas d'une PLL analogique, il est possible d'utiliser un mélangeur pour comparer la phase de deux signaux.

On considère deux signaux à l'entrée d'un mélangeur :

$$V_e = V_{e0} \cos(\omega_e t + \varphi_e) \quad V_s = V_{s0} \cos(\omega_s t + \varphi_s)$$

À la sortie de ce mélangeur, on récupère le produit des deux signaux :

$$V = \frac{V_{e0} V_{s0}}{2} \cos((\omega_e + \omega_s)t + \varphi_s + \varphi_e) + \frac{V_{e0} V_{s0}}{2} \cos((\omega_e - \omega_s)t + \varphi_s - \varphi_e)$$

On obtient une composante basse fréquence qui dépend que du déphasage entre les deux signaux, et une composante à haute fréquence qui va être supprimée par le filtre passe bas. Donc on obtient une tension  $e(t)$  qui dépend du déphasage entre les deux signaux :

$$e(t) = \frac{V_{e0} V_{s0}}{2} \cos((\omega_e - \omega_s)t + \varphi_s - \varphi_e) = E_{max} \cos(\phi_s(t) - \phi_e(t))$$

Cette tension peut être considérée comme l'erreur en fréquence entre les deux signaux Ve et Vs. Et elle constitue une tension de correction pour le VCO.

La caractéristique du VCO est donnée en fonction de la fréquence de VCO à vide  $f_0$ , des fréquences maximum et minimum produites par le VCO, des tensions de commandes maximum et minimum de VCO et de la tension d'entrée  $e(t)$ .

$$f_s(t) = f_0 + K e(t) = f_0 + \delta f \quad \text{Avec : } K = \frac{f_{max} - f_{min}}{e_{max} - e_{min}}$$

La fréquence  $f_s = f_0$  obtenue pour  $e(t) = 0$ , est appelée la fréquence de fonctionnement libre.

La phase instantanée d'un signal sinusoïdal est l'intégrale par rapport au temps de sa fréquence. Donc la phase instantanée de signal de sortie Vs s'écrit :

$$\phi_s(t) = 2\pi \int f_s(t) dt = 2\pi f_0 t + 2\pi K \int e(t) dt$$

La phase de signal de sortie est :  $\varphi_s = 2\pi K \int e(t) dt$

La tension  $e(t)$  commande la fréquence de l'oscillateur pour que la phase instantanée de signal Vs rattrape la phase instantanée de signal d'entrée Ve.

## 4. Fonctionnement de la PLL

### 4.1. PLL non verrouillée

En absence de signal injecté à l'entrée de la boucle, ou si la fréquence du signal injecté est en dehors de la plage de fonctionnement du VCO  $[f_{min}, f_{max}]$ , la boucle est dite non verrouillée et  $f_s = f_0$ .

### 4.2. PLL verrouillée

Si on injecte dans la boucle un signal de fréquence  $f_e$  voisin de  $f_0$ , la PLL se verrouille et on aboutit au bout d'un temps bref à un état stable caractérisé par  $f_s = f_e$ .

La boucle fonctionne sur l'erreur en phase instantanée et comme celle-ci est variable dans le temps, il y'a toujours un écart entre  $\phi_s$  et  $\phi_e$  et l'erreur  $e(t)$  ne peut pas être nulle :  $e(t) = E_{max} \cos(\phi_s - \phi_e)$

A l'équilibre de la boucle, la différence de phase entre l'entrée et la sortie est constante, mais les pulsations sont identiques  $f_s = f_e$ .

### 4.3. Plage de verrouillage (plage de maintien)

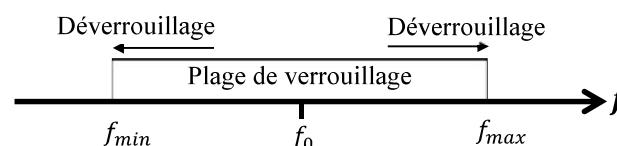

Une fois la boucle verrouillée ou accrochée, la fréquence d'entrée peut varier dans la plage de verrouillage sans que cette boucle ne décroche et on a toujours  $f_s = f_e$ .

La plage de verrouillage correspond à l'écart entre la fréquence  $f_0$  et la fréquence à partir de laquelle la PLL se déverrouille. Elle est limitée par la plage de fonctionnement du VCO ou de la saturation de mélangeur.

Le mélangeur a une tension de saturation  $E_{max}$  à sa sortie, donc la fréquence à la sortie du VCO est :  $f_s = f_0 \pm K E_{max} = f_0 \pm \Delta f$ .

Figure 2 : Plage de verrouillage.

### 4.4. Plage de capture (plage d'accrochage)

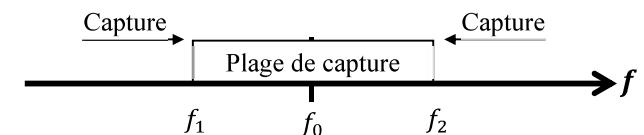

Si la fréquence d'entrée sort de la plage de verrouillage, la boucle décroche et on revient à la situation d'une boucle non verrouillée. Pour raccrocher la boucle, il faut alors revenir au voisinage de  $f_0$  et pénétrer dans la plage de capture.

La plage de capture correspond à l'écart de fréquence entre la fréquence  $f_0$  et la fréquence à partir de laquelle la PLL se verrouille. Elle dépend de  $f_c$ , la fréquence de coupure du filtre passe-bas. Si le battement de fréquence rentre dans la bande passante de filtre, la PLL se verrouille.

Figure 3 : Plage de capture.

### 4.5. Caractéristique de la PLL

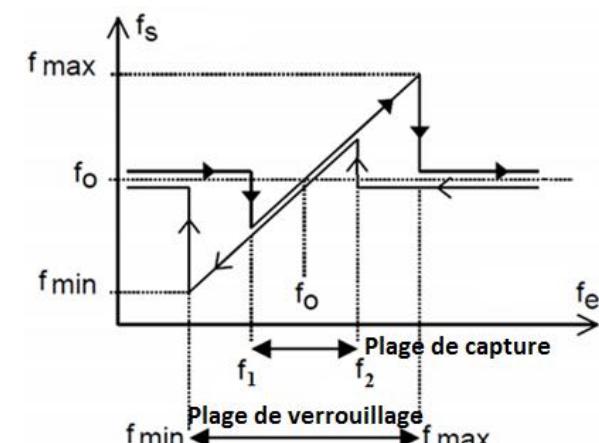

Le fonctionnement de la PLL peut être résumé par sa caractéristique fréquence de sortie en fonction de la fréquence d'entrée.

Figure 4 : Caractéristique de la PLL.

Quand la boucle est verrouillée,  $f_s = f_e$ . Si non,  $f_s = f_0$ .

## 5. Exemple de fonctionnement

Prenons une PLL composée par :

- Un comparateur de phase.

- Un filtre de fréquence de coupure  $f_c=200\text{KHz}$ .

- Un VCO avec une fréquence centrale  $f_0=1\text{MHz}$ ,  $f_{min}=0.5\text{MHz}$  et  $f_{max}=1.5\text{MHz}$  pour une tension de commande allant de  $-2\text{V}$  à  $+2\text{V}$ . La fonction de transfert du VCO s'écrit donc :  $f_S(t) = [1 + 0.25 e(t)] \text{MHz}$

### Boucle non verrouillée

Comme la boucle est non verrouillée elle oscille initialement à la fréquence  $f_0=1\text{MHz}$ .

#### Cas : $f_e < f_0 - f_c$ ( $f_e < 0.8\text{MHz}$ )

On prend par exemple  $f_e=0.6\text{MHz}$ . À la sortie de comparateur, on récupère deux composantes :  $1-0.6 = 0.4\text{MHz}$  et  $1+0.6 = 1.6\text{MHz}$ . Ces deux fréquences sont supérieures à la fréquence de coupure de filtre passe bas  $f_c=200\text{KHz}$  qui va les éliminer.

La tension qui contrôle le VCO est nulle, donc il oscille à la fréquence  $f_0=1\text{MHz}$ . Et la boucle reste non verrouillée.

#### Cas : $f_e > f_0 + f_c$ ( $f_e > 1.2\text{MHz}$ )

Prenons  $f_e=1.3\text{MHz}$ . À la sortie de comparateur :  $1-1.3=0.3\text{MHz}$  et  $(1+1.3)=2.3\text{MHz}$ .

Le filtre passe bas élimine ces deux composantes. Donc, la boucle reste non verrouillée.

#### Cas : $f_e - f_c < f_e < f_0 + f_c$ (Dans la plage de capture)

On prend par exemple  $f_e=0.9\text{MHz}$ . Dans ce cas on obtient à la sortie de comparateur la composante fréquentielle  $1.9\text{MHz}$  qui va être éliminée par le filtre. Et la composante fréquentielle  $0.1\text{MHz}$  qui va contrôler le VCO pour ramener sa fréquence de  $1\text{MHz}$  à  $0.9\text{MHz}$ . Pour cela la tension qui commande le VCO doit être égale à  $-0.4\text{V}$ .

Dans ce cas, la PLL se verrouille sur la fréquence de signal d'entrée  $f_e$ .

### Boucle verrouillée

On suppose que la plage de verrouillage est délimitée par les fréquences de VCO  $f_{min}=0.5\text{MHz}$  et  $f_{max}=1.5\text{MHz}$ .

On considère que la boucle est verrouillée sur la fréquence de signal d'entrée  $f_S = f_e$ .

#### Cas : $f_{min} < f_e < f_{max}$ ( $0.5\text{MHz} < f_e < 1.5\text{MHz}$ : Dans la plage de verrouillage)

On prend par exemple  $f_e=0.6\text{MHz}$ . Quand la boucle est verrouillée :  $f_S = f_e = 0.6\text{MHz}$ .

Le comparateur de phase fournit une composante avec la fréquence  $1.2\text{MHz}$  qui ne peut pas passer par le filtre, et une composante continue :  $e(t) = E \cos(\varphi_S - \varphi_e)$  qui va contrôler la fréquence de sortie de VCO donc de la PLL.

Tant que :  $0.5\text{MHz} < f_e < 1.5\text{MHz}$ , le VCO suit la fréquence de signal d'entrée.

#### Cas : $f_e < f_{min}$ ou $f_e > f_{max}$ ( $f_e < 0.5\text{MHz}$ ou $f_e > 1.5\text{MHz}$ )

Par exemple initialement  $f_S = f_e = 0.5\text{MHz}$ . On suppose que  $f_e$  passe à  $0.4\text{MHz}$ . Le comparateur de phase fournit la composante  $0.9\text{MHz}$  qui va être supprimée par le filtre, et la composante  $0.1\text{MHz}$  qui passe par le filtre mais traduite par une tension  $e(t)$  qui doit indiquer au VCO d'osciller à  $0.4\text{MHz}$ . Comme le VCO ne peut pas osciller à cette fréquence, il revient à  $f_0=1\text{MHz}$  et la boucle se déverrouille.

## 6. Applications

La PLL trouve son utilisation dans plusieurs applications en télécommunications :

- La modulation et la démodulation en fréquence.

- Les systèmes de récupération de porteuse.

- Synthétiseurs de fréquences / Multiplieurs de fréquences.

- Filtres érecteurs de bruit.