## **EX 1:**

A) Soit à décrire en VHDL un additionneur 1 bit schématisé par le bloc suivant :

A et B sont les entrées binaires.

S : résultat de l'addition

C : bit de retenue (carry)

- 1) Etablir la table de vérité de l'additionneur 1 bit.

- 2) Décrire en VHDL, l'entité de l'additionneur qu'on appellera add1.

- 3) Décrire en VHDL, l'architecture flot de données de l'entité add1 avec portes logiques.

- B) L'additionneur précédent est appelé un demi-additionneur.

- 1) Pourquoi?

- 2) Montrer comment peut-on construire un additionneur complet à 1 bit en utilisant un/des demi-additionneur(s).

- 3) Décrire en VHDL, l'entité et l'architecture structurelle de l'additionneur complet.

## EX 2

En utilisant les additionneurs de l'exercice 1, décrire, en VHDL, un additionneur 4 bits.

## **EX 3**:

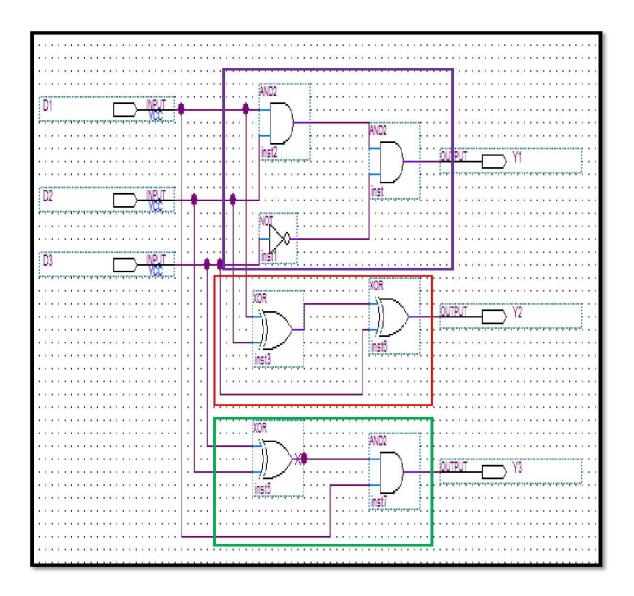

- 1) Décomposer le circuit ci-dessous en 3 circuits et donner pour chacun d'eux une description VHDL en flot de données.

- 2) Décrire en VHDL le circuit complet avec une architecture structurelle.