Université Badji Mokhtar - 2eme année électronique

Matière: TCE1 2023/2024 Enseignant: Dr S.BENSAOULA

# Les circuits intégrés logiques : CMOS

# II.2 La technologie CMOS (Complementary Metal Oxyde Semiconductor)1. Généralités

Ces circuits sont réalisés à partir de transistors à effet de champ de type MOS. Ils sont plus faciles à fabriquer que les circuits de type TTL, permettent une plus grande intégration à grande échelle. L'avantage principal de cette technologie par rapport à la technologie bipolaire est la faible consommation (au détriment de la vitesse).

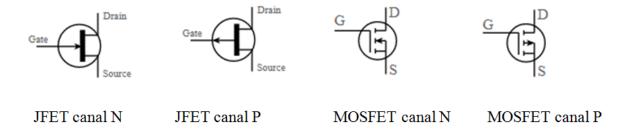

#### Les transistors JFET (ou TEC) et MOSFET

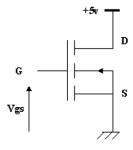

#### Fonctionnement du MOSFET canal N

Rds = résistance drain-source

Si Vgs = 0V,  $Rds = 10^{10} \Omega$ , le transistor est bloqué Si Vgs = +5v,  $Rds = 1000 \Omega$ , le transistor est passant

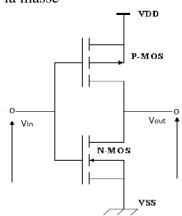

Le fonctionnement du MOSFET canal P est exactement l'opposé de celui à canal N. La technologie CMOS réunit sur le même cristal de silicium, des transistors MOSFET à canal P et à canal N. La figure suivante représente le circuit électronique d'une porte NOT :

$V_{DD}$  = tension d'alimentation,  $V_{SS}$  = la masse

Schéma électronique de la porte NOT

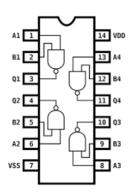

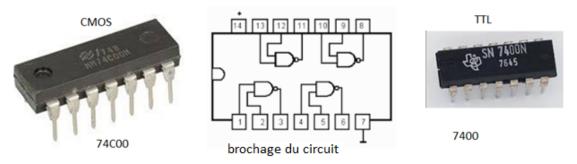

Le circuit intégré CD4011 est un boitier qui renferme 4 portes NAND :

Brochage du CD4011

Le circuit intégré CD4011 de Texas Instrument

Repérage des broches : identique à la technologie TTL.

#### 2. Les familles logiques CMOS

Les avantages de cette famille :

- L'alimentation peut aller de 3V à 18V.

- Le courant d'entrée est nul (consommation nulle), car elle est réalisée avec des transistors à effet de champs. (Les transistors à effet de champs sont commandés en tension).

- Une excellente immunité au bruit.

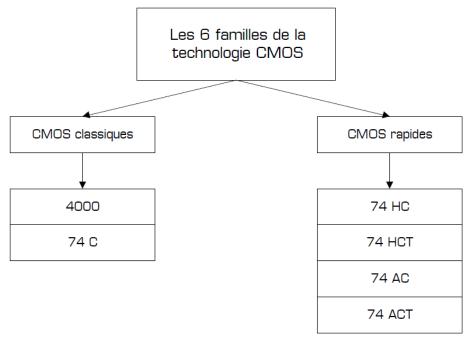

La technologie CMOS se décompose en 6 familles logiques ; on y distingue les CMOS classiques (2 familles) et les CMOS rapides (4 familles) :

Les 2 familles en CMOS classiques :

- $\cdot$  la série 4000 :  $V_{DD}\,$  de 3 à 18 V (série 4000B sorties Bufférisées : courants  $I_{OL}$  et  $I_{OH}$  plus élevées) : la série 4000B est la plus répandue.

- · 74C (même technologie que la série 4000, mais brochage et fonctions de la série TTL 74)

Technologie différentes : même brochage et fonction

Les 4 familles en CMOS rapides : V<sub>DD</sub> de 2 à 6 V (généralement 5V)

- · **74HC** (identique à la série 74C, mais rapide comme la famille TTL LS)

- · 74HCT (identique à la série 74HC, compatibilité totale avec la famille TTL LS)

- · 74AC (CMOS encore plus rapide que la famille HC)

- · **74ACT** (CMOS AC compatible TTL LS)

La compatibilité totale signifie même brochage, même fonction logique et même caractéristiques électriques.

# Signification des lettres C, H, T, et A:

- · C = technologie CMOS

- ·  $\mathbf{H} = \mathbf{H}igh speed = rapidité$

- T = compatibilité totale avec la technologie TTL

- · A = technologie A vanc'e

### Caractéristiques électriques :

$$\begin{split} V_{IHmin} &= 70\%\,V_{DD} & V_{OHmin} &= 95\%\,V_{DD} \\ V_{ILmax} &= 30\%\,V_{DD} & V_{OLmax} &= 5\%\,V_{DD} \end{split}$$

Avant l'utilisation d'un circuit, on doit néanmoins consulter la documentation fournit par le constructeur pour connaître les conditions de son utilisation.

#### Entrées non utilisées :

Les entrées CMOS ne doivent jamais rester non branchées, mais raccordées à une autre entrée utilisée ou mises à la masse ou à VDD à travers une résistance. Une entrée non connectée capte les signaux parasites, ce qui peut se traduire par une plus grande consommation et une surchauffe importante.

#### Découplage des alimentations et type de sortie

On retrouve les mêmes principes que pour la technologie TTL.

En technologie CMOS, on dit drain ouvert et non pas collecteur ouvert comme en TTL.

# III. Immunité aux bruits (marge de bruit) : TTL et CMOS

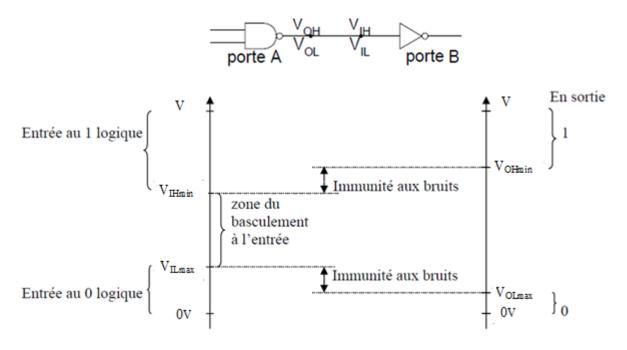

L'immunité aux bruits correspond à l'amplitude de la tension parasite qui peut s'ajouter au signal entre la sortie d'une fonction logique et l'entrée d'une autre fonction logique qui sont reliées, tel que le fonctionnement reste normal.

Correspondance sortie-entrée : marge de bruit

Deux cas peuvent être envisagés

#### Au niveau haut:

Pour que la liaison entre la porte A et la porte B puissent être considérée comme un "1", il faut que  $V_{OH} > V_{OHmin}$  et  $V_{IH} > V_{IHmin}$

Ce qui implique :

$$V_{BH} = (V_{OHmin} - V_{IHmin})$$

On appelle cette tension V<sub>B</sub> la marge de bruit.

#### Au niveau bas:

Pour que la liaison entre la porte A et la porte B puissent être considérée comme un "0", il faut que  $V_{OL} < V_{OLmax}$  et  $V_{IL} < V_{ILmax}$

Ce qui implique:

$$V_{BL} = (V_{ILmax} - V_{OLmax})$$

Lorsque V<sub>B</sub> s'exprime en % de la tension d'alimentation on parle d'immunité au bruit.

#### Exemple:

Technologie TTL, série TTL-LS

$$V_{CC} = 5V$$

,  $V_{OHmin} = 2.7V$ ,  $V_{IHmin} = 2V$ ,  $V_{OLmax} = 0.5V$ ,  $V_{ILmax} = 0.8V$

$$V_{BH} = (V_{OHmin} - V_{IHmin}) = 2.7 - 2 = 0.7V, V_{BL} = (V_{ILmax} - V_{OLmax}) = 0.8 - 0.5 = 0.3V$$

**Etat haut** : si pour la porte A on a  $V_{OH} = 2.7V$ , et si un bruit statique négatif (tension parasite) égale à -0.7V est superposé à  $V_{OH}$ , ce qui donne une tension de 2V. La porte B traduit cette tension à son entrée comme un "1" logique.

$$V_{IH} = V_{OH} + V_{B} = 2.7V + (-0.7V) = 2V$$

Par contre pour  $V_B = -0.8V$ ,  $V_{IH}$  sera dans la zone de non garanti.

**Etat bas** : si  $V_{OL} = 0.2$  V, et si un bruit statique  $V_B = 0.3$ V se superpose à  $V_{OL}$ , on obtient  $V_{IL} = V_{OL} + V_B = 0.3$ V + 0.2V=0.5V

La porte A peut toujours traduire V<sub>IL</sub> comme un '0'

Si par contre  $V_B > 0.3V$ ,  $V_{IL}$  se retrouve dans la zone de non garanti.

#### Remarque:

Les valeurs limites des courants et tensions (min et max), peuvent être atteintes par les grandeurs de tensions et courants, mais il est préférable de les éviter.

# - Comparaison des circuits CMOS et TTL

A l'origine, les circuits CMOS étaient moins rapides que les circuits TTL mais ils avaient une consommation beaucoup moins importante. Néanmoins la consommation des circuits CMOS augmente avec la fréquence. Avec les développements technologiques les différences tendent à disparaitre puisqu'on fabrique des TTL à faible consommation et des CMOS rapides.

Autres avantages de la CMOS, c'est la grande plage de la tension d'alimentation  $V_{DD}$  (de 0 à 18V), ainsi qu'une grande immunité aux bruits.

# VI. Interfaçage

Le problème de l'interfaçage (ou de la compatibilité) peut se poser lorsqu'on veut mélanger plusieurs technologies (TTL-LS, CMOS, HC, etc.) dans un même montage.

Les 2 portes A et B appartiennent à des technologies différentes. La porte A peut commander la porte B si les **deux conditions** suivantes sont de vérifiées:

$$\begin{array}{cc} & V_{OH} > V_{IH} \\ \underline{\textbf{et}} & V_{OL} <_{VIL} \end{array}$$

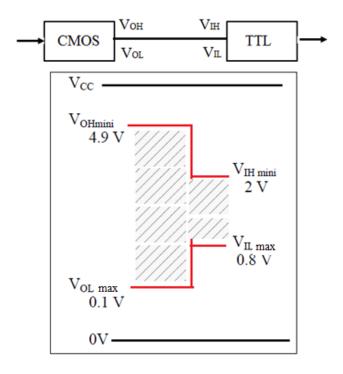

1<sup>er</sup> cas:

Porte A: CMOS

Porte B: TTL standard

Tension d'alimentation :  $V_{CC} = V_{DD} = 5V$

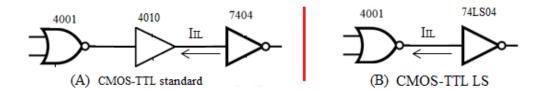

#### **Discussion**

- 1) La zone hachurée correspond à un domaine de fonctionnement non garantie.

- 2) Les gabarits sur cette figure montrent que les 2 conditions précédentes sont vérifiées.

## 3) Etat bas:

La sortie de la CMOS est très proche de zéro volt ( $V_{OLmax}$  =0,05V). La porte TTL voit un niveau bas, elle fournit le courant  $I_{IL}$  qui peut atteindre la valeur  $I_{ILmax}$  = 1,6mA. Ce courant est absorbé par la porte CMOS, et peut générer une chute de tension dans la porte CMOS ( $R_{ds}$ .  $I_{IL}$ ) amenant la tension  $V_{OL}$  à une valeur supérieure à 0,05V. La solution est de placer une porte buffer comme interface (CMOS 4010).

Une porte buffer est capable de fournir ou d'absorber des courants élevés.

Pour le CD4010 on a pour  $V_{DD} = 5V$ :  $I_{OL} = 4mA$ ,  $I_{OH} = 0.4mA$ .

Lorsqu'il s'agit d'une porte TTL LS, ce problème ne se pose pas car pour la TTL LS on a  $I_{ILmax}$ = 0,4mA.

Si  $V_{DD} > 5V$  on doit placer un circuit d'adaptation entre la porte CMOS et la porte TTL.

Si la porte CMOS commande plusieurs entrées TTL, on doit recourir aussi à des circuits d'interface (porte buffer)

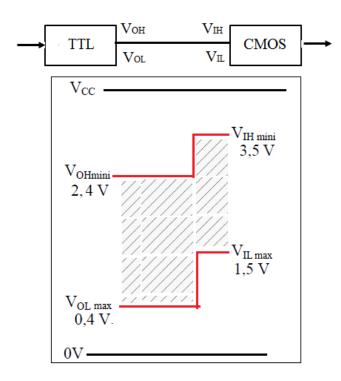

## 2eme cas:

Porte A: TTL standard

Porte B: CMOS

Tension d'alimentation :  $V_{CC} = V_{DD} = 5V$

Comme  $V_{DD} = V_{CC} = 5V$ , il vient :

$$V_{IHmin} = 70\%$$

$V_{DD} = (70x5)/100 = 3.5V$ ,  $V_{ILmax} = 30\% V_{DD} = 1.5V$

Etat bas : la porte TTL peut commander la porte CMOS :  $V_{OLmax} < V_{ILmax}$

$\textbf{Etat haut:} \ la \ porte \ TTL \ ne \ peut \ pas \ commander \ la \ porte \ CMOS \ car: \ V_{OHmin} < V_{IHmin}$

On doit avoir  $V_{OHmin} > V_{IHmin}$

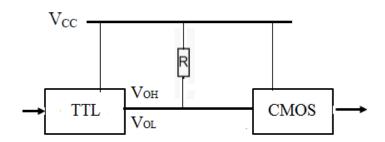

Pour assurer la compatibilité, on utilise une résistance R dite de pull up de l'ordre de  $10~k\Omega$  qui remonte le niveau haut de la TTL.

## Fonctionnement du montage

#### **Etat bas**

$V_{OL}$  < 0,4V, un courant  $I_{OL}$  fournit par l'alimentation traverse R et entre dans la porte TTL. La porte CMOS n'absorbe pas de courant.

#### **Etat haut**

La porte TTL impose un niveau haut et tend à fournir un courant  $I_{OH}$ , comme elle ne peut pas surmonter le potentiel  $V_{CC}$ , et la porte CMOS ne consomme pas de courant, alors aucun courant ne circule et  $V_{OH} = V_{CC} = 5V > V_{IHmin}$ .

$Si\ V_{DD} > 5V$ , on doit placer un circuit d'interface entre les 2 portes afin d'assurer la compatibilité.