### **I.INTRODUCTION**

Data transmission frequently requires conversion operations. Combinatorial circuits are used for this. To create a combinational logic circuit, several elementary logic gates must be used. There are several combinatorial logic devices commonly used in digital systems. These include encoders, decoders, transcoders, multiplexers, demultiplexers, comparators, etc.

# **II. DÉFINITION**

Combinatorial logic concerns the study of functions whose output value depends only on the logical state of the inputs, resulting in a modification of the output value, and not on its previous states: each combination of input variables always corresponds to a single combination of output functions.

The simple gates we have seen so far can be used to build increasingly complex circuits, right up to the most powerful microprocessors.

We are going to look at some of the most common circuits encountered in Systems Architecture.

# **III. COMBINATORIAL CIRCUITS**

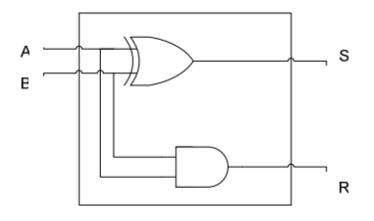

#### **III.1 THE HALF-ADDER :**

The half adder is a combinatorial circuit which can perform the arithmetic sum of two numbers A and B on one bit. The result is the sum S and the carry R.

In binary, addition on a single bit is done as follows:

$$0 + 0 = 00$$

$0 + 1 = 01$

$1 + 0 = 01$

$1 + 1 = 10$

The associated truth table :

| Α | B | R | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

$$R = A.B$$

$$S = \overline{A}.B + A.\overline{B} = A \oplus B$$

Associated Logigram

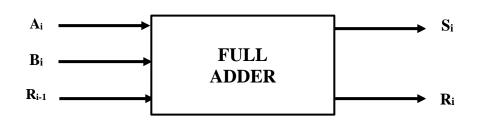

#### **III.2 THE FULL ADDER**

In binary, when you make an addition, you have to take into account the incoming carry.

|    | $r_4$     |           | -           | -     | $r_0 = 0$      |    | r <sub>i-1</sub> |

|----|-----------|-----------|-------------|-------|----------------|----|------------------|

|    |           |           | 2           | $a_2$ | a <sub>1</sub> |    | 0                |

|    | +         | $b_4$     | $b_3$       | $b_2$ | b,             |    | a <sub>i</sub>   |

|    |           | - 4       | - 3         | -2    | -1             | +  | b <sub>i</sub>   |

|    | $r_4$     | $s_4$     | s3          | $s_2$ | s <sub>1</sub> | r, | S;               |

| Th | e one-bit | full adde | er has 3 ir | puts: |                | 1  | 1                |

Computer Science Department - Badji Mokhtar University – Annaba -

#### CHAPTER II

$A_i$ : the first number on a bit.

$B_i$ : the second number on one bit.

R <sub>i-1</sub>: the incoming one-bit carry.

It has two outputs: S: the sum

R<sub>i</sub>: The outgoing Carry

The truth table of one-bit Full Adder :

| a <sub>i</sub> | b <sub>i</sub> | r <sub>i-1</sub> | r | s <sub>i</sub> |

|----------------|----------------|------------------|---|----------------|

| 0              | 0              | 0                | 0 | 0              |

| 0              | 0              | 1                | 0 | 1              |

| 0              | 1              | 0                | 0 | 1              |

| 0              | 1              | 1                | 1 | 0              |

| 1              | 0              | 0                | 0 | 1              |

| 1              | 0              | 1                | 1 | 0              |

| 1              | 1              | 0                | 1 | 0              |

| 1              | 1              | 1                | 1 | 1              |

$$\begin{split} S_i &= \overline{A}_i.\overline{B}_i.R_{i-1} + \overline{A}_i.B_i.\overline{R}_{i-1} + A_i.\overline{B}_i.\overline{R}_{i-1} + A_i.B_i.R_{i-1} \\ R_i &= \overline{A}_iB_iR_{i-1} + A_i\overline{B}_iR_{i-1} + A_iB_i\overline{R}_{i-1} + A_iB_iR_{i-1} \end{split}$$

If we want to simplify the two logical formulas for Si and Ri, we get

$$\begin{split} S_{i} &= \overline{A}_{i}.\overline{B}_{i}.R_{i-1} + \overline{A}_{i}.B_{i}.\overline{R}_{i-1} + A_{i}.\overline{B}_{i}.\overline{R}_{i-1} + A_{i}.B_{i}.R_{i-1} \\ S_{i} &= \overline{A}_{i}.(\overline{B}_{i}.R_{i-1} + B_{i}.\overline{R}_{i-1}) + A_{i}.(\overline{B}_{i}.\overline{R}_{i-1} + B_{i}.R_{i-1}) \\ S_{i} &= \overline{A}_{i}(B_{i} \oplus R_{i-1}) + A_{i}.(\overline{B}_{i} \oplus R_{i-1}) \\ S_{i} &= A_{i} \oplus B_{i} \oplus R_{i-1} \end{split}$$

$$R_{i} = A_{i}B_{i}R_{i-1} + A_{i}B_{i}R_{i-1} + A_{i}B_{i}R_{i-1} + A_{i}B_{i}R_{i-1} + A_{i}B_{i}R_{i-1}$$

$$R_{i} = R_{i-1} \cdot (\overline{A_{i}} \cdot B_{i} + A_{i} \cdot \overline{B_{i}}) + A_{i}B_{i}(\overline{R_{i-1}} + R_{i-1})$$

$$R_{i} = R_{i-1} \cdot (A_{i} \oplus B_{i}) + A_{i}B_{i}$$

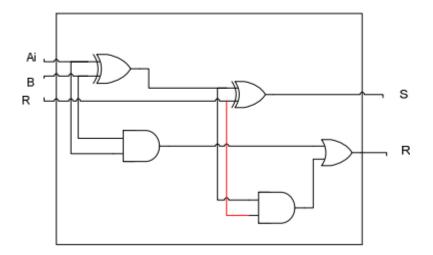

#### The one-bit Full Adder Logigram

$\mathbf{R}_{i} = \mathbf{A}_{i} \cdot \mathbf{B}_{i} + \mathbf{R}_{i-1} \cdot (\mathbf{B}_{i} \oplus \mathbf{A}_{i})$  $\mathbf{S}_{i} = \mathbf{A}_{i} \oplus \mathbf{B}_{i} \oplus \mathbf{R}_{i-1}$

#### CHAPTER II

## **III.3 THE HALF SUBTRACTOR**

The half-subtractor is a combinatorial circuit which performs the arithmetic subtraction of two numbers A and B on one bit. The result is the difference D and the borrow Br.

In binary, single-bit subtraction is performed as follows:

$$\begin{array}{ll} 0-0=0\\ 0-1=1\\ 1-0=0\\ 1-1=0. \end{array}$$

Avec emprunt (Borrow)

6

### The associated truth table

| Α | B | Différence (D) | borrow (Br) |

|---|---|----------------|-------------|

| 0 | 0 | 0              | 0           |

| 0 | 1 | 1              | 1           |

| 1 | 0 | 1              | 0           |

| 1 | 1 | 0              | 0           |

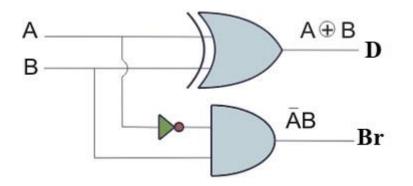

$D = A \oplus B \ et \ Br = \overline{A}B$

The Diagram of the Half Sustractor

#### **III.4 THE FULL SUBSTACTOR**

The one-bit full subtractor has 3 inputs:

$A_i$ : The first number on a bit.

$B_i$ : The second number on a bit

InBr: The Input Borrow

**D:** Difference

$\mathbf{Br}_{:}$  The borrow

| Ai | Bi | Input borrow (InBr) | <b>Difference (D)</b> | Borrow (Br) |

|----|----|---------------------|-----------------------|-------------|

| 0  | 0  | 0                   | 0                     | 0           |

| 0  | 0  | 1                   | 1                     | 1           |

| 0  | 1  | 0                   | 1                     | 1           |

| 0  | 1  | 1                   | 0                     | 1           |

| 1  | 0  | 0                   | 1                     | 0           |

| 1  | 0  | 1                   | 0                     | 0           |

| 1  | 1  | 0                   | 0                     | 0           |

| 1  | 1  | 1                   | 1                     | 1           |

### Truth table for a complete one-bit subtractor

**D** =  $\overline{A} \ \overline{B} \ \text{InBr} + \overline{A} \ \text{B} \ \overline{InBr} + A \ \overline{B} \ \overline{InBr} + A \ \text{B} \ \text{InBr}$

**D** =  $\overline{A}$  ( $\overline{B}$  InBr + B  $\overline{InBr}$ ) + A ( $\overline{B}$   $\overline{InBr}$  + B InBr)

$\mathbf{D} = \overline{\mathbf{A}} \left( \mathbf{B} \bigoplus \mathbf{InBr} \right) + \mathbf{A} \overline{\left( \mathbf{B} \bigoplus \mathbf{InBr} \right)}$

$D = A \oplus B \oplus InBr$

$\mathbf{Br} = \overline{A} \ \overline{B} \ InBr + \ \overline{A} \ B \ \overline{InBr} + \overline{A} \ B \ InBr + A \ B \ InBr$

$\mathbf{Br} = (\overline{A} \ \overline{B} + AB) \operatorname{InBr} + \overline{A} \ B (\overline{InBr} + \operatorname{InBr})$

**Br** =  $(\overline{A \oplus B})$  **InBr** +  $\overline{A}$  **B**

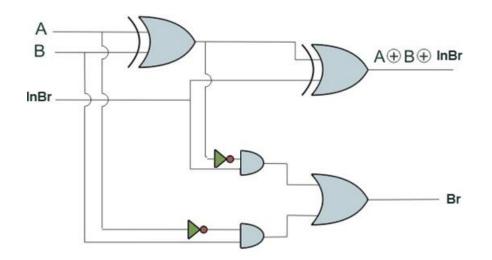

The Full Substractor Diagram

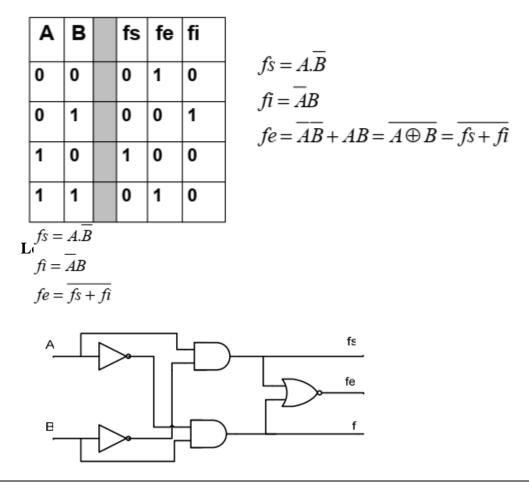

#### **III.4 A ONE BIT COMPARATOR**

A logic comparator is a logic circuit that compares two binary numbers, usually labelled A and B. It has 3 possible outputs noted :

A = B (A equals B)

A > B (A is strictly greater than the number B) and A < B (A is strictly less than the number B) Of which :

If A = B, the output A = B goes to state 1 while the outputs A > B and A < B go to state 0. If the number A is strictly greater than the number B, then the output A > B goes to state 1 while the outputs A = B and A < B go to state 0.

If the number A is strictly less than the number B, only the output A < B goes to state 1.

#### Truth table for a one-bit comparator

fi

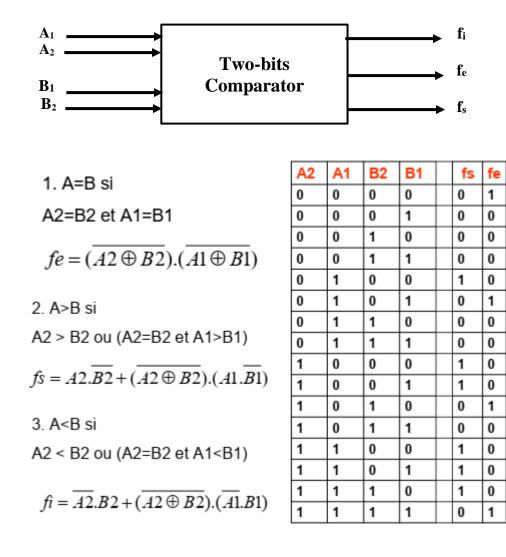

## **III.5 THE TWO-BITS COMPARATOR :**

It compares two numbers A (a2a1) and B (b2b1), each on two bits.

### **III.6 THE MULTIPLEXER**

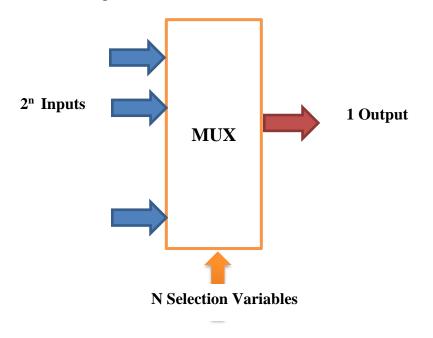

A multiplexer is a logic circuit with several data inputs, but only one output which communicates the data. The routing of input data to the output is controlled by the Select inputs (or address input).

A multiplexer is a combinatorial circuit which can select one item of information (1 bit) from 2n input values.

#### CHAPITRE II

It has :

2n information inputs

A single output

N selection inputs (commands)

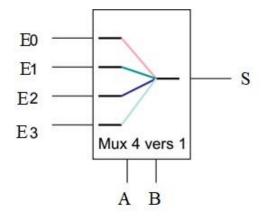

Multiplxer  $4 \rightarrow 1$

## The Truth table

| Α | В | S              |

|---|---|----------------|

| 0 | 0 | Eo             |

| 0 | 1 | E <sub>1</sub> |

| 1 | 0 | E <sub>2</sub> |

| 1 | 1 | E3             |

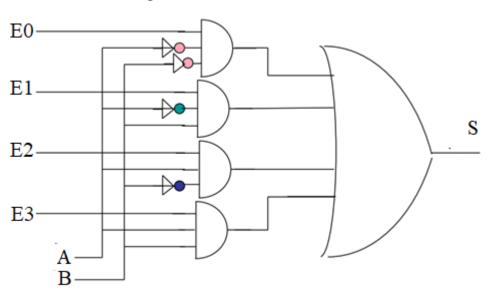

#### $S = \overline{A} \cdot \overline{B} \cdot E_0 + \overline{A} \cdot B \cdot E_1 + A \cdot \overline{B} \cdot E_2 + A \cdot B \cdot E_3$

The Associate Diagram

In this case, there are 4 inputs  $E_0$ ,  $E_1$ ,  $E_2$ ,  $E_3$  which are transmitted to the output according to the choice indicated

by one of the four possible combinations of selection outputs A and B.

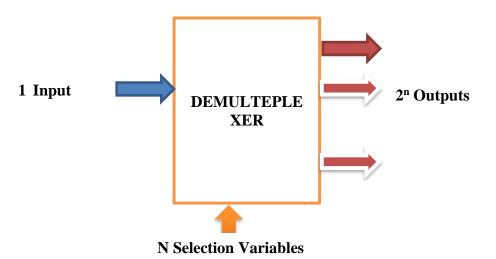

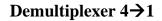

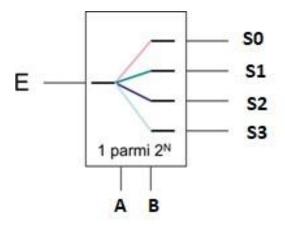

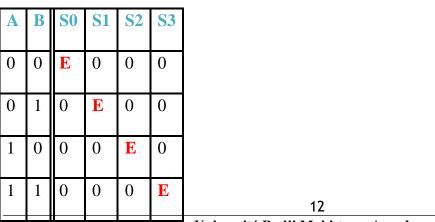

# **III.7 THE DEMULTIPLEXER**

A demultiplexer is a logic circuit with a single input and N output channels. It receives

the input data and chooses to direct it to one of the N possible output channels,

It plays the opposite role to a multiplexer, allowing information to be passed to one of the outputs according to the values of the control inputs

It has :

- ➤ A single input

- > 2n outputs

- $\blacktriangleright$  N selection inputs

Associate Truth Table :

#### Associate Diagram

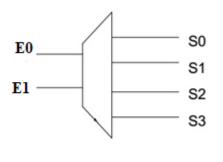

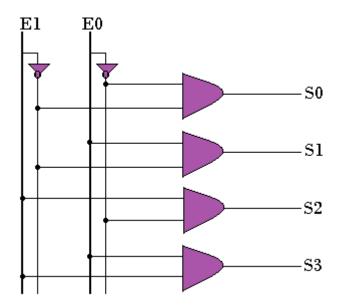

### **III.8 THE BINARY DECODER :**

It is a combinatorial circuit consisting of :

- > N: data inputs

- $\geq$  2n outputs

For each input combination, only one output is active at a time.

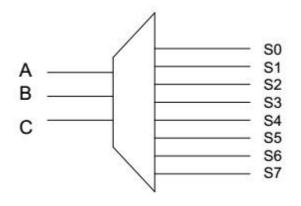

A DECODER  $3 \rightarrow 8$

#### The truth table of a decoder $2 \rightarrow 4$

| <b>E</b> <sub>1</sub> | E <sub>2</sub> | <b>S0</b> | <b>S1</b> | <b>S2</b> | <b>S3</b> |

|-----------------------|----------------|-----------|-----------|-----------|-----------|

| 0                     | 0              | 1         | 0         | 0         | 0         |

| 0                     | 1              | 0         | 1         | 0         | 0         |

| 1                     | 0              | 0         | 0         | 1         | 0         |

| 1                     | 1              | 0         | 0         | 0         | 1         |

$S_0 = \overline{E1}.\overline{E0}, S_1 = \overline{E1}.E0, S_2 = E1.\overline{E0}, S_3 = E1 E0$

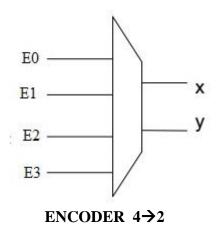

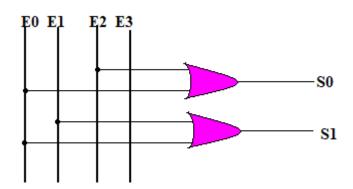

### **III.9 THE BINARY ENCODER**

It plays the opposite role to a decoder, consisting of :

- > 2<sup>n</sup> inputs

- > N outputs

For each input combination we will have its number (in binary) at the output

| E3 | E2 | E1 | E0 | <b>S</b> 1 | S0 |

|----|----|----|----|------------|----|

| 0  | 0  | 0  | 0  | 0          | 0  |

| 1  | 0  | 0  | 0  | 0          | 0  |

| 0  | 1  | 0  | 0  | 0          | 1  |

| 0  | 0  | 1  | 0  | 1          | 0  |

| 0  | 0  | 0  | 1  | 1          | 1  |

$$S1 = E1 + E0 \qquad S0 = E2 + E0$$

#### **III.10** THE PRIORITY ENCODER

Often in an encoder, then called a priority encoder, if several inputs are active simultaneously, in this case we must choose which input bit priority we are going to choose in what follows is a high-order priority encoder.

#### Truth table

| <b>E3</b> | <b>E2</b> | <b>E1</b> | <b>E0</b> | <b>S1</b> | <b>S0</b> |

|-----------|-----------|-----------|-----------|-----------|-----------|

| 0         | 0         | 0         | 0         | 0         | 0         |

| 0         | 0         | 0         | 1         | 0         | 0         |

| 0         | 0         | 1         | 0         | 0         | 1         |

| 0         | 0         | 1         | 1         | 0         | 1         |

| 0         | 1         | 0         | 0         | 1         | 0         |

| 0         | 1         | 0         | 1         | 1         | 0         |

| 0         | 1         | 1         | 0         | 1         | 0         |

| 0         | 1         | 1         | 1         | 1         | 0         |

| 1         | 0         | 0         | 0         | 1         | 1         |

| 1         | 0         | 0         | 1         | 1         | 1         |

| 1         | 0         | 1         | 0         | 1         | 1         |

| 1         | 0         | 1         | 1         | 1         | 1         |

| 1         | 1         | 0         | 0         | 1         | 1         |

| 1         | 1         | 0         | 1         | 1         | 1         |

| 1         | 1         | 1         | 0         | 1         | 1         |

| 1         | 1         | 1         | 1         | 1         | 1         |

After simplification (Karnaugh table)

### $S_1 = E2 + E3$

$S_0 = E3 + \overline{E2} E1$

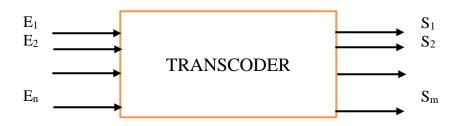

## **III.11 THE TRANSCODER :**

- A transcoder is a combinatorial circuit that transforms an input X code (n bits) into an output Y code (m bits).

A transcoder transforms information available at the input in a given form (generally a code) into the same information, but in another form (generally a different code)

The two most important applications for transcoders are: code conversion and segment display.